# **DIGITAL AUDIO INTERFACE RECEIVER**

### **DESCRIPTION**

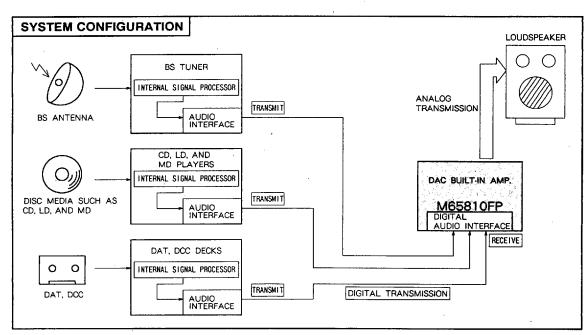

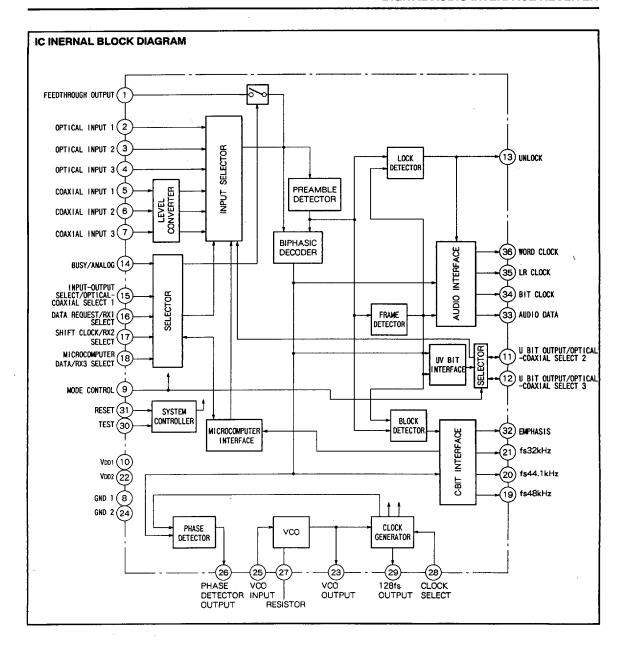

The M65810FP is a semiconductor IC for receiving and decoding digital audio data conforming to the EIAJ (CP-340) standards, transmitted from digital audio equipment such as CD, DAT, DCC, and MD players and BS tuner. It has substantial functions such as built-in input selectors for 6 channels and PLL containing VCO. Furthermore, the IC can read information allotted to serial copy management systems.

#### **FEATURES**

- A total of 6 channels of selectable inputs: 3 channels of optical inputs (CMOS level) and 3 channels of coaxial cable inputs (with a built-in converter to change minimum of 400mVpp into CMOS level) (Selected input is output at the feedthrough pin)

- ■Two kinds of control modes, microcomputer mode using serial data and easy mode using parallel data, are available to choose from as input selection

- Built-in PLL circuit containing VCO

- Selection of master clock from 384fs and 256fs Equipped also with dedicated 128fs output pin

- ■If an error occurs on parity check, the preceding value in audio data is held to prevent noise

- If PLL is unlocked, digital audio data is set to "all O"to mute

- U and V bits are output at dedicated pins (in micro computer mode)

- Word clock output pin gives capability of dealing with diverse kinds of DA converter ICs

### Outline 36P2R-A

0.8mm pitch 450mil SSOP (8.4mm × 15.0mm × 2.0mm)

Outputs C-bit fs information and emphasis information at dedicated pins. The first 32 bits in C-bit data can be read in serial data from in microcomputer mode

#### RECOMMENDED OPERATING CONDITIONS

Supply voltage range  $\cdots$  V<sub>DD</sub> = 4.75 to 5.25V Rated supply voltage  $\cdots$  V<sub>DD</sub> = 5V

6249826 0022580 180 📟

## **DIGITAL AUDIO INTERFACE RECEIVER**

| PIN CONFIGURATION (TOP VIE                   | W)              |                          |  |  |  |  |

|----------------------------------------------|-----------------|--------------------------|--|--|--|--|

|                                              |                 | _                        |  |  |  |  |

| FEEDTHROUGH OUTPUT 1                         | 0               | 36 WORD CLOCK            |  |  |  |  |

| OPTICAL INPUT 1 2                            |                 | 35 LR CLOCK              |  |  |  |  |

| OPTICAL INPUT 2 3                            |                 | 34 BIT CLOCK             |  |  |  |  |

| OPTICAL INPUT 3 4                            |                 | 33 AUDIO DATA            |  |  |  |  |

| COAXIAL INPUT 1 5                            |                 | 32 EMPHASIS              |  |  |  |  |

| COAXIAL INPUT 2 6                            |                 | 31 RESET                 |  |  |  |  |

| COAXIAL INPUT 3 7                            |                 | 30 TEST                  |  |  |  |  |

| GND 1 8                                      | ~               | 29 128fs OUTPUT          |  |  |  |  |

| MODE CONTROL 9                               | M65810FP        | 28 CLOCK SELECT          |  |  |  |  |

| VDD1 10                                      | Ř               | 27 RESISOR               |  |  |  |  |

| U BIT OUTPUT/OPTICAL- COAXIAL SELECT 2       | 70              | 26 PHASE DETECTOR OUTPUT |  |  |  |  |

| U BIT OUTPUT/OPTICAL- 12<br>COAXIAL SELECT 3 |                 | 25 VCO INPUT             |  |  |  |  |

| UNLOCK 13                                    |                 | 24 GND 2                 |  |  |  |  |

| BUSY/ANALOG 14                               |                 | 23 VCO OUTPUT            |  |  |  |  |

| INPUT-OUTPUT SELECT/ 15                      |                 | 22 VDD2                  |  |  |  |  |

| DATA REQUEST/RXI SELECT 16                   |                 | 21 fs32kHz               |  |  |  |  |

| SHIFT CLOCK/RX2 SELECT 17                    |                 | 20 fs44.1kHz             |  |  |  |  |

| MICROCOMPUTER DATA/ 18                       |                 | 19 fs48kHz               |  |  |  |  |

|                                              |                 | .i                       |  |  |  |  |

| 0                                            | Outline 36P2R-A |                          |  |  |  |  |

|                                              |                 |                          |  |  |  |  |

## **DIGITAL AUDIO INTERFACE RECEIVER**

# **DIGITAL AUDIO INTERFACE RECEIVER**

# PIN DESCRIPTION (I ↓ denotes input with pull-down resistor)

| Pin No.    | Symbol           | Name                                             | 1/0          | Hoose                                                                                                                                                                     |         |

|------------|------------------|--------------------------------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 0          | FTO              | Feedthrough output                               | 0            | Usage                                                                                                                                                                     |         |

| 2          | ORX1             | Optical input 1                                  | l i          | Through output of selected RX                                                                                                                                             |         |

| 3          | ORX2             | Optical input 2                                  | i            | CMOS level inputs                                                                                                                                                         |         |

| 4          | ORX3             | Optical input 3                                  | <u> </u>     | CIVICO IBVBI INDUIS                                                                                                                                                       |         |

| ⑤          | CRX1             | Coaxial input 1                                  | i i i        |                                                                                                                                                                           |         |

| 6          | CRX2             | Coaxial input 2                                  | i i          | Inputs to internal level converter                                                                                                                                        |         |

| 7          | CRX3             | Coaxial input 3                                  | i            | Minimum input voltage 400mVP-P                                                                                                                                            |         |

| 8          | VSS1             | GND 1                                            | _            |                                                                                                                                                                           |         |

| 9          | MODE             | Mode control                                     |              | H = microcomputer mode, L = easy mode                                                                                                                                     |         |

| 0          | V <sub>DD1</sub> | Voot                                             | _            | made and mode, E - easy mode                                                                                                                                              |         |

| 0          | UBO/<br>OCSEL2   | U bit output/optical-<br>coaxial select 2        | 0            | In microcomputer mode:U-bit data output(in synchronization with LF in easy mode: RX1 optical line/coaxial line input selector. H = optical line input                     | RCK)    |

| 10         | VBO/<br>OCSEL3   | U bit output/optical-<br>coaxial select 3        | 0            | In microcomputer mode:V-bit data output(in synchronization with LF In easy mode: RX2 optical line/coaxial line input selector, H = optical line input                     | RCK)    |

|            | UNLOCK           | Unlock                                           | 0            | PLL unlock information : unlock = H                                                                                                                                       |         |

| 09         | BUSY/ANALOG      | Busy/analog                                      | o<br>1↓/0    | In microcomputer mode:modification information about C-bit data co<br>modefication=H<br>In easy mode:RX inputs are all shout off on a H pulse and VCO also                |         |

| 15         | 10SEL/0CSEL1     | Input-output select/<br>optical-coaxial select 1 |              | In microcomputer mode:data input/output selector, H=microcomputer→DAI,L=DAI→microcomputer In easy mode:RX3 optical line/coaxial line input selector, H=optical line input |         |

| 16         | REQ/<br>RX1SEL   | Data request/<br>RX1 select                      | 1↓/0         | In microcomputer mode: data input/output enabled at H In easy mode: RX1 is selected on H pulse and H is held                                                              |         |

| Ø          | SCK/<br>RX2SEL   | Shift clock/<br>RX2 select                       | 1 → /0       | In microcomputer mode: data is shifted on a fall In easy mode: RX2 is selected on H pulse and H is held                                                                   |         |

| 189        | MDATA/<br>RX3SEL | Microcomputer data/<br>RX3 select                | I↓/0<br>I↓/0 | In microcomputer mode: serial data input/output                                                                                                                           |         |

|            | FS48             | fs48kHz                                          | 0            | Set by C-bit fs code: 48kHz = L These are a                                                                                                                               |         |

| <b>20</b>  | F\$44            | fs44.1kHz                                        | 0            | Set by C-bit fs code: 44.1kHz = L to H under                                                                                                                              |         |

| 20         | FS32             | fs32kHz                                          | 0            | Set by C-bit fs code: 32kHz = L condition.                                                                                                                                | UI HOCK |

| <b>Ø</b>   | V <sub>DD2</sub> | V <sub>DD2</sub>                                 | _            | Power supply to VCO                                                                                                                                                       |         |

| 8          | VCOO             | VCO output                                       | 0            | =384fs or 256fs(according to the polarity of pin 39)master clock of                                                                                                       | utput   |

| 29         | VSS2             | GND 2                                            |              | Ground of VCO. Same voltage as VSS1.                                                                                                                                      |         |

| 8          | VCOI             | VCO input                                        | 1            | VCO control voltage input                                                                                                                                                 |         |

| <b>₩</b>   | PD0              | Phase detector output                            | 0            | Forms an external loop filter                                                                                                                                             | -       |

| Ø          | R1               | Resistor                                         | _            | Adusts free-running oscillation frequency by resistor for adjustment of VCO oscillation frequency                                                                         |         |

| _ <b>8</b> | CKSEL            | Clock select                                     | i            | Master clock frequency selector: H = 384fs, L = 256fs                                                                                                                     |         |

| 8          | 128FS            | 128fs output                                     | 0            | 128fs clock output                                                                                                                                                        |         |

| 30         | TEST             | Test                                             |              | Test pin. Normally fixed to L, TEST = H                                                                                                                                   |         |

| 3)         | RESET            | Reset                                            | l l          | Initialization at power up. RESET = L                                                                                                                                     |         |

| 8          | EMP              | Emphasis                                         | 0            | Set by C-bit emphasis code: 50/15 μ sec = H                                                                                                                               |         |

| 3          | ADATA            | Audio data                                       | 0            | 16-bit audio data serial output (MSB first)                                                                                                                               |         |

| 39         | BCK              | Bit clock                                        | 0            | Audio data shift clock = 64fs                                                                                                                                             |         |

| <b>3</b> 9 | LRCK             | LR clock                                         | 0            | = fs                                                                                                                                                                      |         |

| - 89       | WCK              | Word clock                                       | 0            | = 2fs (50 % duty)                                                                                                                                                         |         |

### **DIGITAL AUDIO INTERFACE RECEIVER**

## ABSOLUTE MAXIMUM RATINGS (Ta = 25 °C, unless otherwise noted)

| Symbol               | Parameter                               | Ratings                  | Unit |

|----------------------|-----------------------------------------|--------------------------|------|

| V <sub>DD</sub> -Vss | Suply voltage                           | - 0.3 to 6.5             | ٧    |

| Vpo1-Vpo2            | Voltage difference between VDD 1 and 2. | ± 0.3                    | V    |

| Vı                   | Input voltage                           | Vss - 0.3 to $Vdd + 0.3$ | ٧    |

| Pd                   | Power dissipation                       | 1100                     | mW   |

| Topr                 | Operating temerature                    | - 20 to + 70             | ಌ    |

| Tstg                 | Storage temperature                     | - 40 to + 125            | ొ    |

## RECOMMENDED OPERATING CONDITIONS

| Symbol Parameter | Test conditions                 |           | Limits              |       |        |          |

|------------------|---------------------------------|-----------|---------------------|-------|--------|----------|

|                  |                                 | Min       | Тур                 | Max   | Unit   |          |

| VDD              | Suplly voltage                  |           | 4.75                | -     | 5.25   | >        |

| VIH              | Input voltage (H level)         |           | 0.7 V <sub>DD</sub> | 1     | Vpb    | <b>V</b> |

| VIL              | Input voltage (L level)         |           | Vss                 | -     | 0.3Vpp | <b>V</b> |

| fvco             | Oscillation frequency (VCO)     | CKSEL = L | -                   | 256fs | -      | 1        |

| fvco             | Oscillation frequency (VCO)     | CKSEL = H | -                   | 384fs | -      | 1        |

| fs               | Input signal sampling frequency |           | 32                  | _     | 48     | kHz      |

## ELECTRICAL CHARACTERISTICS (DC CHARACTERISTICS)

| Symbol Parameter |                            | Tank and distance                                 |         | Limits     |     |      |

|------------------|----------------------------|---------------------------------------------------|---------|------------|-----|------|

|                  | Parameter                  | Test conditions                                   |         | Тур        | Max | Unit |

| loo              | Circuit current            | When receiving fs = 44.1kHz                       | _       | 20         | -   | mA   |

| Voн              | Output voltage (H level)   | IoH = - 500 µA                                    | VDD - 1 | -          | -   | ٧    |

| Vol              | Output voltage (L level)   | loL = 500 μA                                      | -       | _          | 0.4 | V    |

| lin              | Input leak current         | V <sub>1</sub> = V <sub>SS</sub> ~V <sub>DD</sub> | -       | <b>—</b> . | ± 1 | μΑ   |

| loL              | Driver current             | Vol. = 0.5V, pins (9/29/2)                        | 15      |            | _   | mΑ   |

| Юн               | Driver current             | $V_{OH} = V_{DD} - 1.5V$ , pins (4)(6)(7)(8)      | 15      | _          | _   | mA   |

| Rid              | Input pull-down resistance | Pins (19/66/17/18)                                | 20      | _          | 100 | kΩ   |

# **DIGITAL AUDIO INTERFACE RECEIVER**

# FUNCTION DESCRIPTION 6 channel input selector

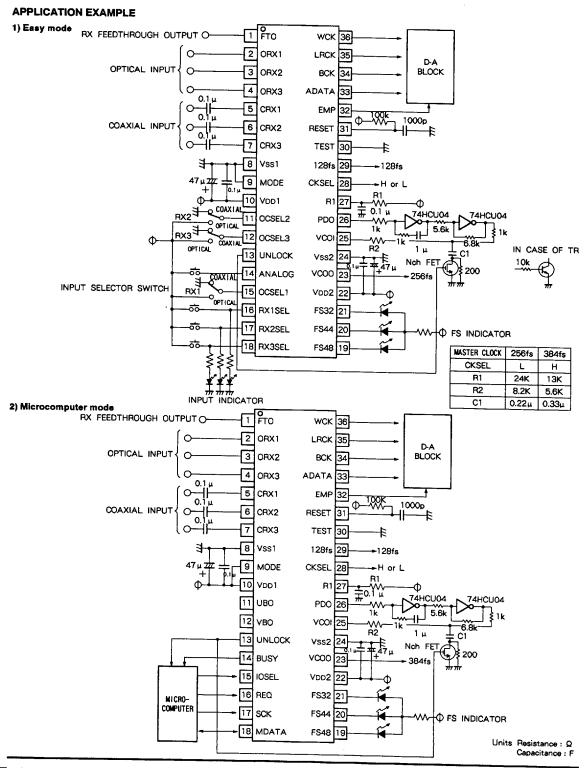

### 1. Easy mode (MODE=L)

| inpu             | t    | 0 | CSE |   | RX1SEL   | RX2SEL     | RX3SEL   | ANALOG   |

|------------------|------|---|-----|---|----------|------------|----------|----------|

|                  |      | Ľ | 2   | 3 |          |            |          |          |

|                  | ORX1 | Τ | _   | - |          | _          | -        | -        |

| Optical<br>input | ORX2 | - | Н   | - | _        | <b>-</b> _ | -        | -        |

| ,                | ORX3 | - | -   | Н | 1        |            | <b>-</b> | _        |

|                  | CRX1 | L | 1   | - | <u>_</u> | _          | -        | _        |

| Coaxial<br>input | CRX2 | - | ب   | 1 | -        | <b>-</b> - | _        | -        |

|                  | CRX3 | - |     | Г | 1        | _          |          | -        |

| Analog r         | node | - | _   | - | 1        | 1          | -        | <b>-</b> |

- RX inputs are selected at the positive-going edge of a H pulse inputted to the RX1SEL to RX3SEL pins. As the H level is held therefrom, they can be used for indicator lamps and the like.

- If a H pulse is inputted to the ANALOG pin, the analog mode takes place at the positive-boing edge of the H pulse.

None of RX inputs are accepted and VCO stops.

- If a H pulse is inputted to RX1SEL to RX3SEL in analog mode, a predetermined RX input is selected at the positivegoing edge of the H pulse, and VCO oscillation starts.

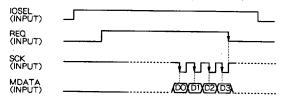

## 2. Microcomputer mode (MODE=H)

In microcomputer mode, it is possible to select RX inputs during input mode (IOSEL = H: microcomputer -> DAI)

Data is taken into the IC at the negative-going edge of SCK, and then is latched at the negative-going edge of REQ. According to the last 4 bits, selection of RX inputs and control of feedthrough output are carried out.

| Input         | D1   | D2 | D3 |   |

|---------------|------|----|----|---|

|               | ORX1 |    | Н  | Н |

| Optical input | ORX2 | Н  | Н  | Ļ |

|               | ORX3 |    | L  | Н |

|               | CRX1 | L  | H  | Н |

| Coaxial input | CRX2 |    | Н  | L |

|               | CRX3 |    | L  | Н |

| Analog mo     | Х    | L  | L  |   |

# None of RX inputs are accepted and VCO stops in analog mode.

The feedthrough output (FTO) is turned ON/OFF by the polarity of DO.

| DO                                           | FTO              |

|----------------------------------------------|------------------|

| <u>       L                             </u> | ON               |

| H                                            | OFF (fixed to L) |

## 3. Input signal voltage range

| Optical input | (ORX1 to 3)           | Coaxial input | (CRX1 to 3) |

|---------------|-----------------------|---------------|-------------|

| L level       | H level               | Min           | Max         |

| 0.3VDDmax     | 0.7V <sub>DDmin</sub> | 400mVp-p      | 5VP-P       |

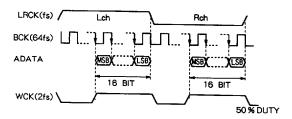

### **Audio interface**

### 1. Audio format

MSB first, last 16 bit

### 2. Audio data output timing

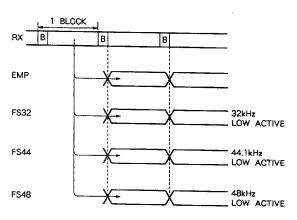

### C-Bit data output timing

### 1. Output through dedicated pins

6249826 0022585 762 1

### DIGITAL AUDIO INTERFACE RECEIVER

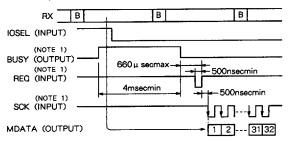

## 2.Serial data output in microcomputer mode (MODE=H)

In microcomputer mode, it is possible to read out the first 32 bits in C-bit data during output mode (IOSEL = L : DAI→ microcomputer)

Note 1.BUSY gose high if the first 32 bits in C-bit data change, compared with the previous block. It gose back low if consecutive 2 blocks consist of the same content.

Consequently, the minimum H pulse width of BUSY is 4ms (when fs = 48kHz).

If BUSY gose high, read out C-bit data after detecting the negative-going edge of BUSY because new contents of C-bit data transferred to the output register are the beginning of the next block.

Note 2. As the first 32 bits in C-bit data are loaded to the output register at the inverting edge of REQ, be sure to invent REQ before reading out C-bit data. SCK is taken into the IC only when REQ is high, so that REQ should be constantly retained high while reading.

As BUSY compulsively goes back low at the inverting edge of REQ, let REQ go high within 660 µs (the shortest time at which BUSY may go high next) after a fall of BUSY so as to make sure that next BUSY is detected.

If it is impossible to meet the 660 µs requirement due to the timer a microcomputer has, it is recommended to use both kinds of operation, to read with BUSY and to read C-bit data periodically (every several milliseconds to several tens of milliseconds) independently of BUSY.

Note 3. To read out C-bit data, set SCK to high level at the positive-going edge of REQ.

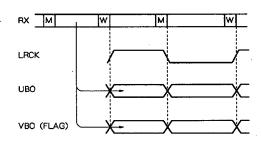

### U-Bit/V-bit data output timing

### Reset

By resetting after power up, it is possible to arrange the following initial settings.

### 1. In easy mode

The RX1 input is selected. Optical/coaxial lines are selected by the polarity of OCSEL 1 to 3.

#### 2. In microcomputer mode

The ORX1 (optical line) input is selected.

# **DIGITAL AUDIO INTERFACE RECEIVER**

6249826 0022587 535

### **DIGITAL AUDIO INTERFACE RECEIVER**

### **EIAJ STANDARD FORMAT**

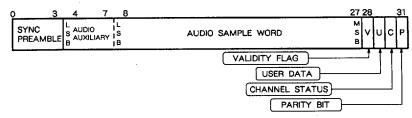

(Fig. 1) Subframe format

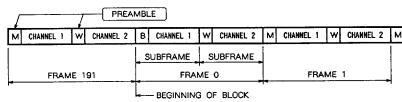

(Fig. 2) Frame format

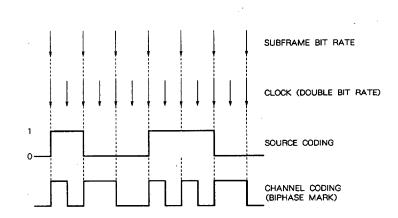

(Fig. 3) Biphasic mark system

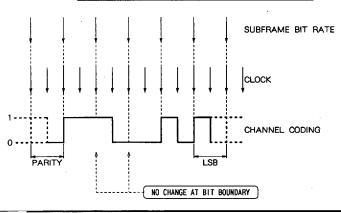

### (Table 1) Preamble channel coding

| Preamble  | Channel coding       |                      |  |  |

|-----------|----------------------|----------------------|--|--|

| 1 Teamble | Precedence symblol:0 | Precedence symblol:1 |  |  |

| "B"       | 11101000             | 00010111             |  |  |

| "M"       | 11100010             | 00011101             |  |  |

| "W"       | 11100100             | 00011011             |  |  |

(Fig. 4) Preamble "M"

6249826 0022588 471